FPGA 프로그래밍 블록세트

dSPACE 시스템에서의 FPGA 모델 통합

FPGA 프로그래밍 블록세트는 이전 Xilinx System Generator Blockset인 Xilinx ® Vitis™ Model Composer HDL Library를 사용하여 dSPACE 시스템으로 생성된 FPGA 모델을 사용하기 위한 Simulink ® 블록세트입니다.

-

FPGA 프로그래밍 블록세트 2023-A – 새로운 기능

- FPGA 모델을 프로세서 모델에 쉽게 연결(Simulink ® , ConfigurationDesk)

- 모델 기반 I/O 구성

- Simulink에서의 오프라인 시뮬레이션

적용 분야

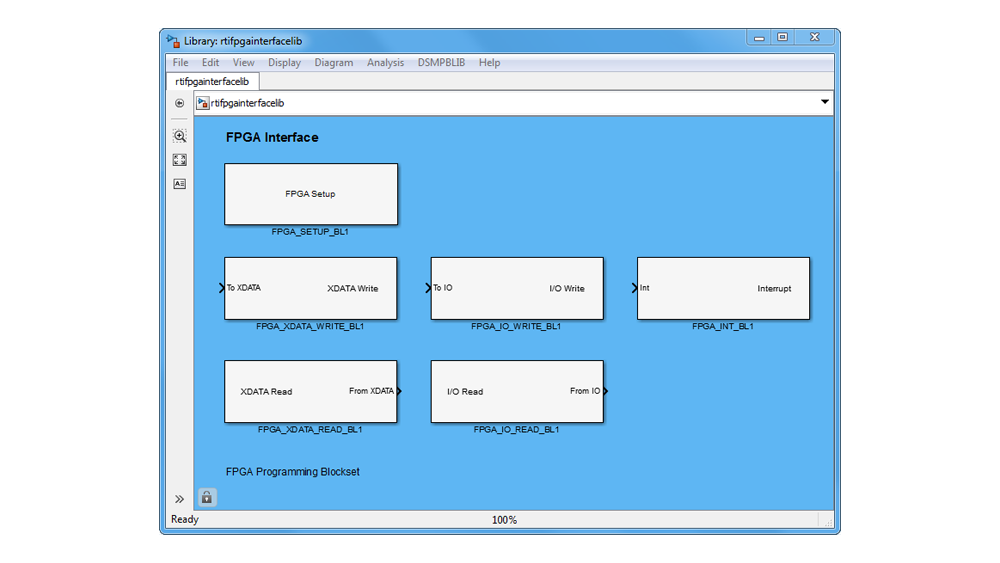

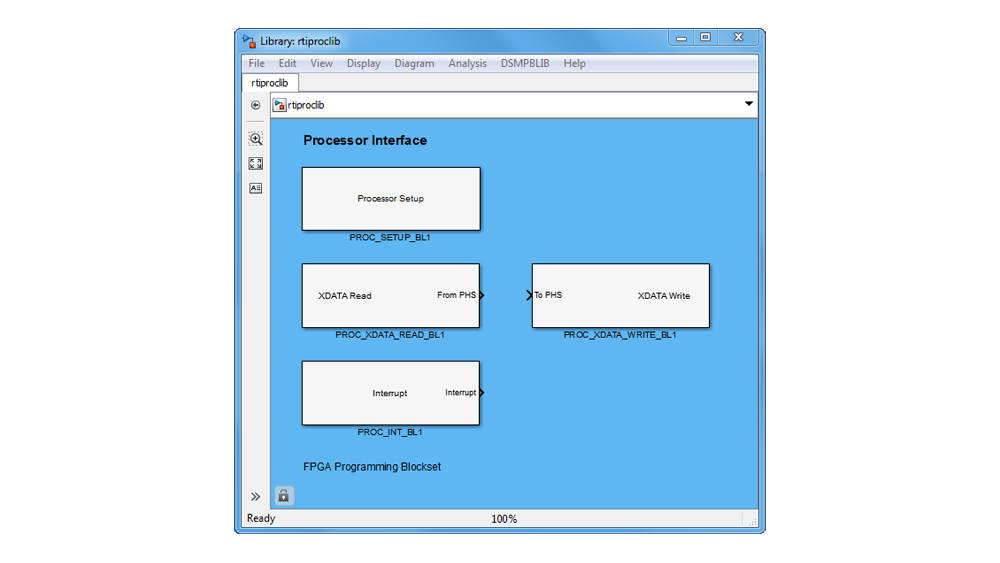

FPGA 프로그래밍 블록세트는 이전 Xilinx System Generator Blockset인 Xilinx ® Vitis™ Model Composer HDL Library를 사용하여 dSPACE 시스템으로 생성된 FPGA 모델을 사용하기 위한 Simulink 블록세트입니다. 이는 dSPACE 보드에 장착된 FPGA와 I/O 간의 인터페이스, dSPACE FPGA 보드와 연산 노드 간의 인터페이스를 구현하기 위한 블록을 제공합니다.

이 블록세트는 사용자 프로그래밍 가능 FPGA를 제공하는 다음의 dSPACE FPGA 플랫폼과 함께 사용할 수 있습니다.

- DS2655 FPGA 베이스 보드 및 해당 I/O 모듈

- DS6601/DS6602 FPGA 베이스 보드 및 해당 I/O 모듈

- I/O 모듈로 확장된 MicroAutoBox II 1401/1511/1514 및 1401/1513/1514

- I/O 모듈로 확장된 MicroAutoBox III 1403/1511/1514 및 1403/1513/1514

- MicroLabBox

RCP 및 HIL(Hardware-in-the-Loop) 시뮬레이션을 위한 일반적인 애플리케이션 시나리오는 다음과 같습니다.

- 자동차, 산업 자동화, 의료 엔지니어링 및 항공 우주 산업의 프로젝트

-

전기 파워트레인을 위한 신호 전처리, 새로운 인터페이스 채택, 매우 빠른 제어 루프, 새로운 컨셉 설계 및 테스트

주요 이점

dSPACE FPGA 플랫폼은 Simulink ® 의 Xilinx Vitis™ Model Composer HDL Library를 사용하여 그래픽으로 프로그래밍할 수 있는 다양한 첨단 Xilinx ® FPGA를 제공합니다.

FPGA 프로그래밍 블록세트를 사용하면 결과 FPGA 설계를 dSPACE 하드웨어에서 실행되는 실시간 애플리케이션에 통합할 수 있습니다.

또한 블록세트는 I/O 보드의 I/O 드라이버 구성 요소를 연결하고 프로세서 기반 계산 노드(SCALEXIO 처리 하드웨어, MicroLabBox 또는 MicroAutoBox)에 대한 연결을 모델링하는 편리한 방법을 제공합니다. 데이터 교환은 고정 소수점 데이터 형식은 물론 부동 소수점 데이터 형식도 지원합니다.

FPGA 애플리케이션을 개발하는 데 있어 최대한의 자유를 보장하기 위해 VHSIC 하드웨어 설명 언어(VHDL 또는 Verilog)의 핸드코드 인터페이스를 사용하여 전체 설계를 핸드코딩할 수도 있습니다. 또는 손으로 쓴 IP 코어를 Simulink FPGA 모델에 통합하거나 MathWorks ® HDL Coder TM 를 사용하여 FPGA 설계의 일부를 모델링할 수도 있습니다.

FPGA 블록세트를 사용하면 Simulink에서 직접 FPGA 또는 프로세서를 합성, 구축 및 프로그래밍하여 최적의 편의성을 얻을 수 있습니다. 실행 시간 동안 모델을 수정하지 않고도 변수에 액세스하여 추적하거나 수정할 수 있습니다. FPGA 범위를 사용하면 설계에 대한 심층 분석도 가능합니다.

| 하드웨어 옵션 | 보드 및 변형 |

|---|---|

| SCALEXIO |

|

| MicroAutoBox |

|

| MicroLabBox |

|

| 기능 | 설명 |

|---|---|

| 일반 |

|

| FPGA 인터페이스 |

|

| 핸드코드 인터페이스 |

|

| I/O 액세스 |

|

| 프로세서-FPGA 통신 |

|

| SCALEXIO FPGA 베이스 보드 사이의 FPGA 간 통신 |

|

| 비동기 작업 |

|

| 변수 액세스 |

|

| 원격 FPGA 빌드 |

|

| MathWorks ® HDL Coder TM 지원 |

|

혁신을 추진하세요. 항상 기술 개발의 동향을 주시해야 합니다.

저희 전문 지식 서비스에 가입하세요. dSPACE의 성공적인 프로젝트 사례를 확인해 보세요. 시뮬레이션 및 검증에 대한 최신 정보를 받아보세요. 지금 바로 dSPACE 다이렉트(뉴스레터)를 구독하세요.